# 2 Channel H Bridge Constant Voltage/Constant Current Driver

www.onsemi.com

#### Overview

The LB1939T is a two-phase excitation bipolar stepping motor driver that features low voltage operation, a low saturation voltage, and low power consumption. It supports constant voltage and constant current drive, can control two iris motors, and is optimal for shutter, iris, and AF drive in 3 V battery operated still digital cameras and other battery operated equipment.

#### **Features**

- · Low-voltage drive

- Dual power supply operation: VS = 1.6 to 7.5 V,  $V_{DD} = 1.9$  to 6.5 V

- Single power supply operation:  $VS = V_{DD} = 1.9$  to 7.5 V

- $\bullet$  Low saturation voltage output: Vosat = 0.3 V at  $I_O$  =  $200\,mA$

- Supports constant voltage and constant current drive

- Built-in reference voltage circuit (Vref = 0.9 V)

- Miniature, thin form package (Thickness t = 1.1 mm)

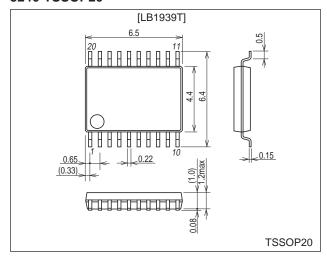

## **Package Dimensions**

unit: mm

#### 3246-TSSOP20

## **Specifications**

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                                 | Symbol            | Conditions                               | Ratings       | Unit |

|-------------------------------------------|-------------------|------------------------------------------|---------------|------|

| Maximum supply voltage                    | V <sub>Bmax</sub> | VS1, VS2, V <sub>DD</sub>                | -0.3 to +10.5 | V    |

| Applied output voltage                    | V <sub>OUT</sub>  | OUT1, 2, 3, 4                            | -0.3 to +10.5 | V    |

| Maximum output current: OUT1, 2, 3, and 4 | I <sub>Omax</sub> | t ≤ 10 ms                                | 400           | mA   |

| Applied input voltage                     | V <sub>IN</sub>   | ENA, IN, VC                              | 10.5          | V    |

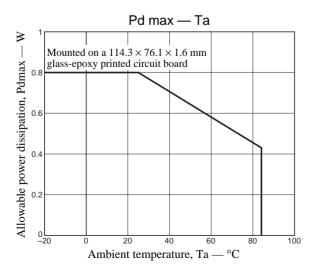

| Allowable power dissipation               | Pdmax             | When mounted on a printed circuit board* | 0.8           | W    |

| Operating temperature                     | Topr              |                                          | -20 to +85    | °C   |

| Storage temperature                       | Tstg              |                                          | -55 to +150   | °C   |

Note: Circuit board: 114.3  $\times$  76.1  $\times$  1.6  $mm^{\scriptscriptstyle 3}$  glass epoxy board

# Allowable Operating Conditions at $Ta = 25^{\circ}C$

| Parameter                            | Symbol             | Conditions                         |      | - Unit |      |       |  |

|--------------------------------------|--------------------|------------------------------------|------|--------|------|-------|--|

| Farameter                            | Symbol             | Conditions                         | min  | typ    | max  | Offic |  |

| Operation guaranteed voltage range 1 | V <sub>OPR</sub> 1 | V <sub>DD</sub> system, VS = 2.0 V | 1.9  |        | 6.5  | V     |  |

| Operation guaranteed voltage range 2 | V <sub>OPR</sub> 2 | VS system, V <sub>DD</sub> = 5.0 V | 1.6  |        | 7.5  | V     |  |

| Input low-level threshold voltage    | V <sub>IL</sub>    | ENA1, ENA2, IN1, IN2               | -0.3 |        | +1.0 | V     |  |

| Input high-level threshold voltage   | V <sub>IH</sub>    | ENA1, ENA2, IN1, IN2               | 2.0  |        | 6.0  | V     |  |

# Electrical Characteristics at $Ta=25^{\circ}C,\,VS=3.0\;V,\,V_{DD}=5.0\;V$

| Darameter                                                     | Cumbal             | Conditions                                                                                                         |      | Ratings |      |      |  |

|---------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------|------|---------|------|------|--|

| Parameter                                                     | Symbol             | Conditions                                                                                                         | min  | typ     | max  | Unit |  |

| Standby mode current drain                                    | I <sub>STB</sub>   | VS = V <sub>DD</sub> = 6.5 V                                                                                       |      | 0.1     | 1.0  | μA   |  |

| [Regulator Output Circuit]                                    |                    |                                                                                                                    |      |         |      |      |  |

| V <sub>REF</sub> output voltage                               | V <sub>REF</sub>   | I <sub>OL</sub> = 0 to 1 mA                                                                                        | 0.85 | 0.9     | 0.95 | V    |  |

| SV <sub>DD</sub> output voltage                               | VSV <sub>DD</sub>  | I <sub>OL</sub> = 10 mA                                                                                            | 4.7  | 4.8     |      | V    |  |

| [H Bridge Output Circuit]                                     |                    |                                                                                                                    |      |         |      |      |  |

| OUT pin output saturation voltage 1 (Saturation control mode) |                    | $V_{DD}$ = 5.0 V, VC = SV <sub>DD</sub> , VS = 2.0 V<br>$I_{O}$ = 200 mA (PNP transistor side)                     |      | 0.20    | 0.30 | V    |  |

| OUT pin output saturation voltage 2 (Saturation control mode) | Vosat2             | $V_{DD}$ = 5.0 V, VC = SV <sub>DD</sub> , VS = 2.0 V<br>$I_{O}$ = 200 mA (NPN transistor side)                     |      | 0.10    | 0.15 | ٧    |  |

| OUT pin output voltage 1 (Constant voltage control mode)      | V <sub>OUT</sub> 1 | $V_{DD} = 6.0 \text{ V}, VC = 1.5 \text{ V}, VS = 3.5 \text{ V}$<br>$I_{O} = 200 \text{ mA}$ (PNP transistor side) | 2.8  | 2.9     | 3.0  | V    |  |

| OUT pin output voltage 2 (Constant voltage control mode)      | V <sub>OUT</sub> 2 | $V_{DD}$ = 6.0 V, VC = $V_{REF}$ , VS = 2.0 V<br>$I_{O}$ = 200 mA (PNP transistor side)                            | 1.65 | 1.75    | 1.85 | V    |  |

| OUT pin output current 1 (Constant current control mode)      | I <sub>OUT</sub> 1 | $V_{DD}$ = 6.0 V, VC = 0.9 V, VS = 3.5 V<br>RL = 5 $\Omega$ (between OUT and OUT), RFB = 1 $\Omega$                | 197  | 210     | 223  | mA   |  |

| OUT pin output current 2 (Constant current control mode)      | l <sub>OUT</sub> 2 | $V_{DD}$ = 6.0 V, VC = $V_{REF}$ , VS = 2.0 V<br>RL = 5 $\Omega$ (between OUT and OUT), RFB = 1 $\Omega$           | 189  | 210     | 231  | mA   |  |

| VS system operating current drain 1                           | I <sub>S</sub> 1   | VC = SV <sub>DD</sub>                                                                                              |      | 4       | 7    | mA   |  |

| VS system operating current drain 2                           | I <sub>S</sub> 2   | VC = VREF                                                                                                          |      | 1.5     | 3    | mA   |  |

| V <sub>DD</sub> system operating current drain 1              | I <sub>DD</sub> 1  | VC = SV <sub>DD</sub> ENA1 = 2 V                                                                                   |      | 4       | 7    | mA   |  |

| V <sub>DD</sub> system operating current drain 2              | I <sub>DD</sub> 2  | VC = V <sub>REF</sub> ENA1 = 2 V                                                                                   |      | 4       | 7    | mA   |  |

| VC input voltage range                                        | VC                 |                                                                                                                    | 0.1  |         | 7    | V    |  |

| VC input current                                              | IVC                | V <sub>DD</sub> = 6.0 V, VS = 2.0 V, VC = 5.0 V                                                                    | 0    | 50      | 100  | μA   |  |

| [Control Input Circuit]                                       |                    |                                                                                                                    |      |         |      |      |  |

| Control pin maximum input current                             | I <sub>IH</sub>    | V <sub>IH</sub> = 5.5 V 70                                                                                         |      | 100     | μA   |      |  |

| Control pin maximum input current                             | I <sub>IL</sub>    | V <sub>IL</sub> = GND                                                                                              | -1   |         | 0    | μA   |  |

## **Truth Table**

| Input   |                                             |   |                                    | Output |   |    |   |      |                                   |  |

|---------|---------------------------------------------|---|------------------------------------|--------|---|----|---|------|-----------------------------------|--|

| EI      | NA                                          | I | N                                  |        | 0 | UT |   | SVDD | Mode                              |  |

| 1       | 2                                           | 1 | 2                                  | 1      | 2 | 3  | 4 | 3,00 |                                   |  |

| L       | L                                           |   |                                    |        |   |    |   |      | Standby mode (zero current drain) |  |

| Н       |                                             | Н |                                    | L      | Н |    |   | on   | Channel 1: reverse                |  |

|         |                                             | L |                                    | Н      | L |    |   | on   | Channel 1: forward                |  |

|         | н                                           |   | Н                                  |        |   | L  | Н | on   | Channel 2: reverse                |  |

|         | П                                           |   | L                                  |        |   | Н  | L | on   | Channel 2: forward                |  |

| Blank e | Blank entries indicate "don't care" states. |   | Blank entries indicate off states. |        |   |    |   |      |                                   |  |

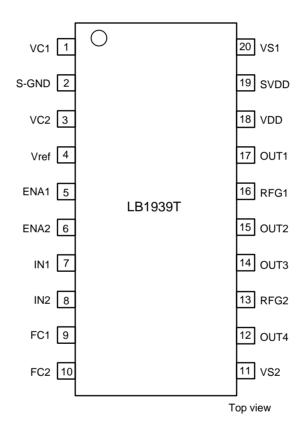

# Pin Assignment

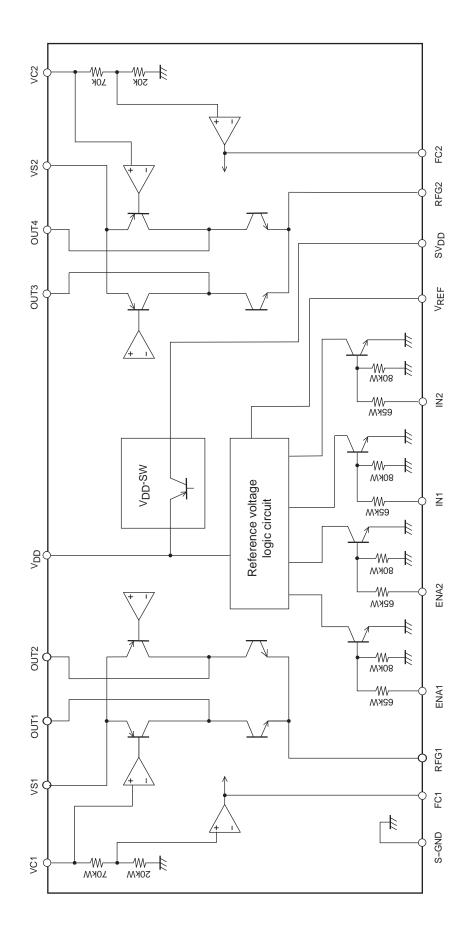

# **Block Diagram**

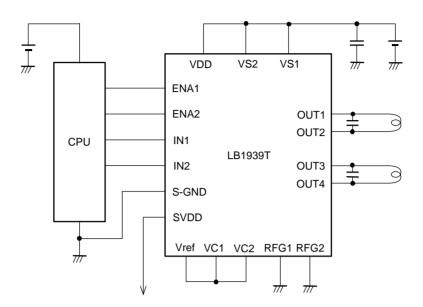

#### **Application Circuit Example 1**

Constant voltage control mode: OUT outputs a 1.75 V, which is Vref (0.9 V)  $\times$  1.95.  $\ast$  : FC1 and FC2 are left open.

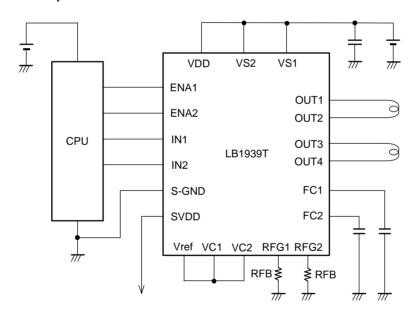

## **Application Circuit Example 2**

Constant current control mode: The RFG voltage is controlled so that Vref/4.5 = 0.2 V.

Therefore, when RfB is 1  $\Omega$ , the circuit operates in constant current drive with lcoil = 0.2 V/1  $\Omega$  = 200 mA.

\*: There are no magnitude constraints on the inputs (ENA, IN) and the supply voltages ( $V_{DD}$ ,  $V_{S}$ ). For example, the IC can be operated at  $V_{IN} = 5$  V,  $V_{DD} = 3$  V, and  $V_{S} = 2$  V.

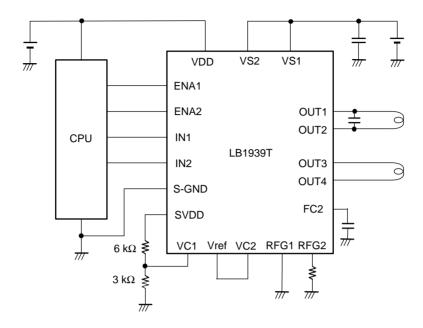

#### **Application Circuit Example 3**

Channel 1 operates in constant voltage control mode: OUT outputs  $V_{DD} \times 3K/(3K + 6K) \times 1.95$ Channel 2 operates in constant current control mode: The RFG voltage is controlled so that Vref/4.5 = 0.2 V. \*: FC1 is left open.

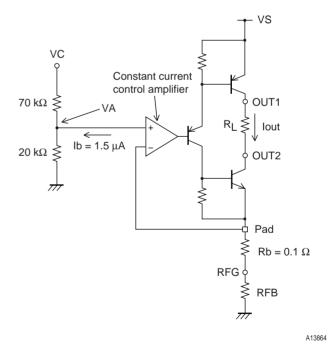

#### **Notes on Constant Current Control Settings**

The LB1939T constant current control circuit has the structure shown in the figure at the right. The voltage input to the VC pin is resistor divided internally (by 70 k $\Omega$  and 20 k $\Omega$  resistors) to 1/4.5 and input to the plus (+) input of the constant current control amplifier as reference.

The minus (–) input of this constant current control amplifier is connected, through the wire bond resistor Rb (=  $0.1~\Omega$ ), to the RFG pin. The constant current control circuit operates by comparing the voltage generated by the external current detection resistor connected to the RFG pin and the reference voltage mentioned above.

Note that the voltage at VA will be that given by the following formula since the bias current Ib (=  $1.5~\mu A$ ) flows from the constant current control amplifier plus (+) input during constant current control operation.

$$VA = VC/4.5 + Ib \times 20 \text{ k}\Omega$$

$$= VC/4.5 + 0.03$$

Therefore, the logical expression for setting the constant current Iout is as follows.

Iout =

$$VA/(RFB + Rb)$$

=  $(VC/4.5 + 0.03) / (RFB + Rb) .....(1)$

#### **Constant Current Control Usage Notes**

This IC supports both constant current control and constant voltage control modes. However, since both of these control circuits operate at all times, certain of the limitations imposed by the constant voltage control circuit apply may when using constant current control.

For example, if constant current control is used with the application circuit example 2, if VC = 0.9 V (= Vref) and RFB =  $1 \Omega$ , then the output current can be calculated as follows from (1) on the previous page.

```

Iout = (0.9/4.5 + 0.03) / (1 + 0.1)= 0.23/1.1\approx 0.209A

```

Here, if the value driven load resistance RL is r, since the RFG pin voltage is 0.23 V and the npn transistor output saturation voltage is 0.1 V (typical), the pnp transistor output pin voltage can be calculated as follows.

```

Vout = (RFG pin voltage) + (npn transistor output saturation voltage) + (voltage across the load terminals)

= 0.23 + 0.1 + 0.209 \times r

= 0.3 + 0.209r

```

At the same time, however, this IC's internal constant voltage control circuit controls the output voltage as follows.

```

Vout' = VC \times 1.95 \approx 1.75 \text{ V}

```

Therefore, it will not be possible to use the constant current control mode if the value of r is set so that Vout is greater than Vout'. That is, the condition

```

0.33 + 0.209r > 1.75

```

implies that

This means that constant current control can be used when the value of the load resistance used is strictly less than  $6.79\,\Omega$ .

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent re